積體電路

負微分電阻電路(NDR)設計應用、類比積體電路設計

以IC製作為主要訴求,研究發展內容包括負微分電阻、壓控震盪器(VCO) 、鎖相迴路(PLL)、除頻器(FD)與多值記憶器等等,經由學習過程讓學生學會Spice 、Layout、Testing等等IC開發的本質才能。

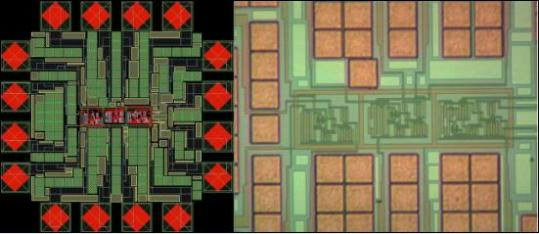

IC Layout圖與IC晶片微影圖

近年內執行計畫

- 以新型架構實現單穩態-雙穩態傳輸邏輯閘電路之分析、設計與應用(I)。(國科會計畫,NSC100-2221-E-415-012,100/08~101/07,計畫主持人)。

- 以混沌現象為基礎的高頻除頻器電路與低功率多值邏輯電路之設計與應用。(國科會計畫,NSC99-2221-E-415-016,99/08~100/07,計畫主持人)。

- 以矽鍺積體電路製程實現多峰值負微分電阻電路的新奇應用(II)。(國科會計畫,NSC97-2221-E-168-045,97/08~98/07,計畫主持人)。

- 以差動放大器設計與製造寬頻壓控振盪器。(國科會計畫,NSC97-2221-E-168-046,97/08~98/07,計畫共同主持人)。

- 以矽鍺積體電路製程實現多峰值負微分電阻電路的新奇應用(I)。(國科會計畫,NSC96-2221-E-168-033,96/08~97/07,計畫主持人)。

- 開發新型MOS-BJT-NDR元件與應用積體電路之設計(3/3)。(國科會計畫,NSC95-2221-E-168-037,95/08~96/07,計畫主持人)。

- 開發新型MOS-BJT-NDR元件與應用積體電路之設計(2/3)。(國科會計畫,NSC94-2215-E-168-001,94/08~95/07,計畫主持人)。

- 以負微分電阻元件實現高頻壓控振盪器電路。(國科會計畫,NSC94-2815-C-168-005–E, 94/07~95/02,計畫指導教授)。

- 開發新型MOS-BJT-NDR元件與應用積體電路之設計(1/3)。(國科會計畫,NSC93-2215-E-168-002,93/08~94/07,計畫主持人)。

- 利用BiCMOS製程來設計與製作高調變性的負微分電阻元件與應用電路。(國科會計畫,NSC92-2218-E-168-005,92/08~93/07,計畫主持人)。

- 適合CMOS與BiCMOS製程的負微分電阻元件及應用積體電路之研究。(國科會計畫,NSC91-2215-E-168-001,91/08~92/07,計畫主持人)。

- 研製以電晶體構建的S型與N型負微分電阻元件,應用電路,與其積體電路化之探討。(國科會計畫,NSC90-2215-E-168-002,90/08~91/07,計畫主持人)。

- 互動式電腦網路輔助模擬與教學系統-負電阻半導體元件原理,設計與應用。(國科會計畫,NSC90-2516-S-168-001,90/08~91/07,計畫主持人)。

- 電腦輔助設計-類似Esaki二極體之N型負微分電阻元件串接電路之電流-電壓特性,磁滯現象與其應用電路之研究。 (國科會計畫,NSC89-2215-E-168-005,89/08~90/07,計畫主持人)。

- 電腦輔助設計-研究負微分電阻元件串接電路之結合電流-電壓特性。(國科會計畫,NSC89-2215-E-168-003,88/08~89/07,計畫主持人)。